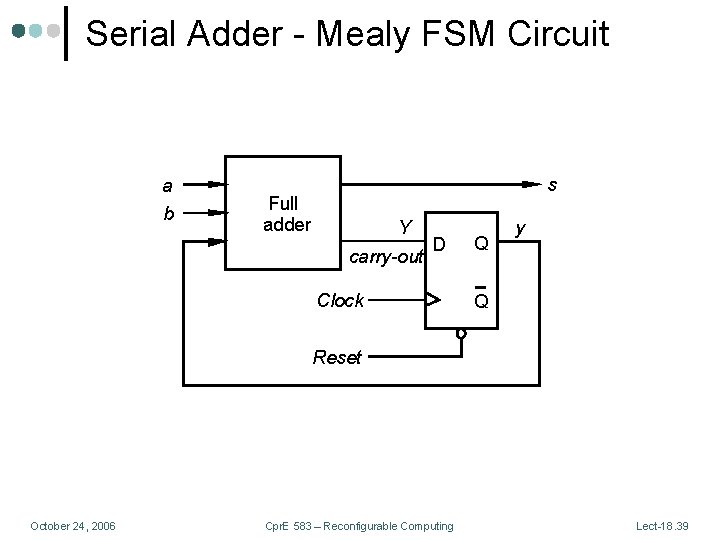

Vhdl Code For Serial Adder Using Finite State Machine

This page consists of design examples for state machines in VHDL. A state machine is a sequential circuit that advances through a number of states. The examples provide the HDL codes to implement the following types of state machines:

- 4-State Mealy State Machine

- This VHDL project presents a car parking system in VHDL using Finite State Machine (FSM). VHDL code and testbench for the car parking system are fully provided. The VHDL car parking system is shown in the following figure. There is a front sensor to detect vehicles going to the gate of the car parking system.

- Assume that i want to add 4 signals a,b,c,d and i want to add them using adder2 which adds to signals only.and i want to implement them in adder tree format so in the first state a, and b will be added and saved at signal y and c and d will be added as well and saved at signal z then in the next state y and z will be added and and the result will be at the the output x.

FSM Part 1 A finite-state machine (FSM) or simply a state machine is used to. Let x = 4'b1100 Nov 01, 2017 Verilog code for an N-bit Serial Adder with. Using Mealy and Moore State Machine VHDL Codes. Feb 29, 2012 VHDL Code Examples for Flip Flop, Serial to Parallel Converter, 4 bit Counter, State Machine, and ADDER VHDL Code Examples VHSIC Very High Speed Integrated Circuits Hardware Description Language IEEE-1076. Using the FSM VHDL code template provided above, you will implement a Finite State Machine in its canonical implementation. Moreover, you should be able to implement you own Vending Machine in VHDL! If you appreciated this post, please help us to share it with your friend.

The outputs of a Mealy state machine depend on both the inputs and the current state. When the inputs change, the outputs are updated without waiting for a clock edge.

- 4-State Moore State Machine

The outputs of a Moore state machine depend only on the present state. The outputs are written only when the state changes (on the clock edge).

- Safe State Machine

This example uses the syn_encoding synthesis attribute value safe to specify that the software should insert extra logic to detect an illegal state and force the state machine's transition to the reset state.

- User-Encoded State Machine

This example uses the syn_encoding synthesis attribute to apply specific binary encodings to the elements of an enumerated type.

Download the files used in this example:

Each zip download includes the VHDL file for the state machine and its top level block diagram.

Related Links

Design Examples Disclaimer

These design examples may only be used within Intel devices and remain the property of Intel Corporation. They are being provided on an “as-is” basis and as an accommodation; therefore, all warranties, representations, or guarantees of any kind (whether express, implied, or statutory) including, without limitation, warranties of merchantability, non-infringement, or fitness for a particular purpose, are specifically disclaimed. Intel expressly does not recommend, suggest, or require that these examples be used in combination with any other product not provided by Intel.

VHSIC [Very High Speed Integrated Circuits] Hardware Description Language

IEEE-1076

This is just a quick reference of some short VHDL code fragments. Above each code segment is a circuit which represents the fragment.

In most cases the Process, and end of Process commands are not listed to keep the text down.

VHDL code for a D Flip Flop

process (signal names)

begin

if (clock’event and clock = ‘1’) then

output <= data;

end if;

end process

A 1 bit flip flop is used as the example. but any data width may be used.

Reference; a D Flip Flop Definition and true table.

VHDL code for a D Flip Flop with Reset and Clear

if reset = ‘0’ then

output <= ‘0’;

elsif set = ‘0’ then

output <= ‘1’;

elsif (clock’event and clock = ‘1’) then

output <= data;

end if;

Note that the code show asynchronous Reset and Clear lines, which is fine for the code segment.

However those lines should be synchronized at some point, or insure that no data is used when those lines are valid.

VHDL code for a D Flip Flop

if (clock’event and clock = ‘0’) then

if (reset = ‘0’ and data = ‘0’) then

output <= ‘0’;

elsif (reset = ‘0’ and data = ‘1’) then

output <= ‘0’;

elsif (reset = ‘1’ and data = ‘0’) then

output <= ‘0’;

elsif (reset = ‘1’ and data = ‘1’) then

output <= ‘1’;

end if;

Another flip flop using a reset, but this time just to zero out the data, as in a gating signal.

Again, the rest signal should have been synchronized with the clock at some point [in another code fragment].

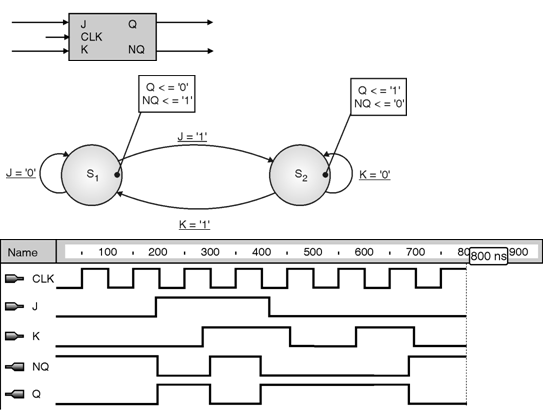

VHDL code for a JK Flip Flop

if (clock’event and clock = ‘1’) then

if (in1 = ‘0’ and in2 = ‘0’) then

output <= output;

elsif (in1 = ‘1’ and in2 = ‘0’) then

output <= ‘1’;

elsif (in1 = ‘0’ and in2 = ‘1’) then

output <= ‘0’;

elsif (in1 = ‘1’ and in2 = ‘1’) then

output <= not(output);

end if;

end if;

Reference; a JK Flip Flop Definition and true table.

VHDL code for a 2-to-1 Mux

if sel = ‘0’ then

output <= data1;

elsif sel = ‘1’ then

output <= data2;

end if;

Reference Standard Logic Multiplexer Circuits.

This circuit may be scaled to any data width, and more complicated select functions can be implemented.

VHDL code for a Serial to Parallel Converter

if clear = ‘0’ then

shift_reg <= “00000000”;

elsif (clock’event and clock = ‘1’) then

shift_reg(7 downto 1) <= (6 downto 0);

shift_reg(0) <= serial;

end if;

A common 8 bit data path is coded as an example.

Reference Common Shift Register Functions.

VHDL code for a Parallel to Serial Converter

if load = ‘0’ then

shift_reg <= parallel;

elsif (clock’event and clock = ‘1’) then

serial <= shift_reg(7);

shift_reg(7 downto 1) <= (6 downto 0);

end if;

A common 8 bit data path is coded as an example.

Reference Common Shift Register Functions.

VHDL code for a 4 bit Counter

if load = ‘0’ then

output <= “1111”;

elsif (clock’event and clock = ‘1’) then

output <= data - ‘1’;

end if;

carry <= ‘0’ when output = “0000” else‘1’;

load <= carry;

The code provides a 4 bit down counter function.

Reference common logic functions; Up/Down Decade Counters, or Up/Down Binary Counters.

VHDL code for a 1 bit Adder

if c = ‘0’ then

if (a and b) = ‘1’ then

sum <= ‘0’;

carry <= ‘1’;

elsif (a or b) = ‘1’ then

sum <= ‘1’;

carry <= ‘0’

end if;

elsif c = ‘1’ then

if (a and b) = ‘1’ then

sum <= ‘1’;

carry <= ‘1’;

elsif (a or b) = ‘1’ then

sum <= ‘0’;

carry <= ‘1’;

end if;

end if;

An adder could be a half adder which does not accept a carry in or a full adders that uses a carry input [as shown].

It's assumed that these inputs are some how synchronized with a clock.

Reference; Types of IC Adders, with logic diagram.

VHDL code for a State Machine

if reset = ‘0’ then

state <= stateA;

output <= ‘0’;

elsif (clock’event and clock) = ‘1’ then

case state is

when stateA

output <= ‘0’;

state <= stateB

when stateB

output <= ‘1’;

if input = ‘1’ then

state <= stateB;

else

state <=stateC;

end if;

when stateC

output <= ‘0’

state <= stateA;

end case;

Exclusive-OR Gate

if (a and b) = ‘1’ then

y <= ‘0’;

elsif (a and b) = ‘0’ then

y <= ‘0’;

else

y <= ‘1’;

end if;

Reference; a Exclusive-OR Gate Definition and true table.

IEEE-1076: Standard VHDL Language Reference Manual IEEE Computer Society Document

IEEE 1076.1: VHDL Analog and Mixed-Signal Extensions IEEE Computer Society Document

IEEE 1076.2: Standard VHDL Mathematical Packages IEEE Computer Society Document

IEEE 1076.3: Standard VHDL Synthesis Packages IEEE Computer Society Document

IEEE 1076.4: Standard for VITAL ASIC (Application Specific Integrated Circuit) Modeling Specification IEEE Computer Society Document

IEEE 1076.6: Standard for VHDL Register Transfer Level (RTL) Synthesis IEEE Computer Society Document

Links on this site:

VHDL Sites: Listed here

Back to the Logic Design Page, Digital Logic Pitfalls

VHDL Design Tools: CAD - CAE Products

VHDL Simulation Tools: VHDL Simulation Software Products

FPGA Manufactures: Hardware - Components - Semiconductor- Digital - Programmable Logic

Serial Adder Verilog

In regards to flip-flops and other examples, there are no constraints on using standard functions.

That is a flip flop does not have to be constrained to a D-type or JK-type function, any number of commands might be used.

The functions provided do relate to an available IC function so comparisons can be made between the firmware and hardware.

Vhdl Code For Serial Adder Using Finite State Machine Programming

| Home | |||||||

| Distributors | Components | Equipment | Software | Standards | Buses | Design | Reference |

© 1998 - 2016 All rights reserved Larry Davis